#### Muhaned Zaidi

Al-Manara College for Medical Sciences, Missan, Iraq E-mail: muhanedzaidi@uomanara.edu.iq

#### **Highlights:**

- Two operational amplifier topologies and two compensation strategies were compared in this study ECG as the application of focus.

- The bulk-driven MOS transistor technique was used to provide a low supply voltage and avoid voltage threshold effects.

- The first operational amplifier design was a typical two-stage amplification design with standard Miller compensation, while the second design was a two-stage amplification design with two integrated compensation approaches (standard Miller and negative Miller compensation).

- To improve the unity gain frequency and phase margin of the second -amp while keeping power consumption constant, negative Miller compensation was applied by connecting a capacitor between the input and output nodes of the bulk-driven first stage as well as standard Miller compensation in the second stage.

Two Abstract: bulk-driven CMOS (Complementary Metal Semiconductor) operational amplifier (op-amp) designs for electrocardiogram (ECG) application are presented and compared in this paper. Both op-amps are based on two-stage amplification, where bulk-driven differential input is the first stage, while additional DC gain is the second stage. Different compensation techniques were integrated in each op-amp design. Standard Miller compensation was used for the first op-amp parallel with the second stage. The novelty of the second op-amp is that it utilizes negative Miller compensation between the bulkdriven input node and the output node of the first stag, while standard Miller compensation was used in the second stage. The purpose of this work was to compare DC gain, phase margin (PM) and unit gain frequency (UGF) obtained through different simulated compensation strategies and test results. The op-amps were simulated using 0.25 μm CMOS technology. The simulation results are presented using the standard model libraries from Tanner EDA tools, operating on a single rail +0.8V power supply.

**Keywords**: bulk-driven; ECG; low power; Miller compensation; negative Miller compensation; op-amp; unity gain frequency.

Copyright ©2022 Published by ITB Institute for Research and Community Services, ISSN: 2337-5779,

DOI: 10.5614/j.eng.technol.sci.2022.54.5.10

#### 1 Introduction

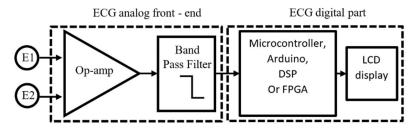

An electrocardiogram (ECG) is a classic test to detect cardiac problems. The ECG technique is completely non-invasive, painless, and provides doctors and patient with immediate results. Nowadays, ECG is a technology that must be smaller and more portable, easier to use, affordable to create, and have a long battery life [1]. The basic diagram of an ECG is shown in Figure 1, where sensors E1 and E2 detect the electrical pulse of the heart, which is used to determine the ECG signal from the human body. In Figure 1, the control circuit of the ECG design contains two parts: firstly, the analog front-end ECG component (an integrated circuitopamp) that is used to amplify the ECG signal; secondly, an analog to digital converter (ADC) for digitizing the analog ECG signal and a digital to analog converter (DAC) for the display system for tracking the heart rate of the patient. Other elements that help connect the ECG signal are based on using either electronic programmable device such as a microcontroller ( $\mu$ C) [2], an Arduino [3], a digital signal processor (DSP) [4, and a field-programmable gate array (FPGA) [5].

Figure 1 Traditional ECG sensor design.

One of these electronic parts is the operational amplifier (op-amp. The greatest challenge in designing the op-amp is dealing with a situation where power and voltage diminish, prompting a decrease in the performance of the amplifier. For example, reduced power consumption leading to a decreased frequency response performance (such as unity gain frequency (UGF) or slew rate (SR)) at high speed [6, because UGF and SR are current dependent [7].

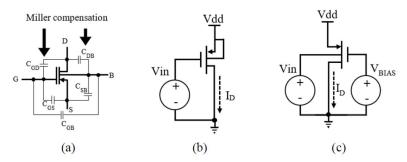

The simple analog front-end consists primarily of an instrumentation amplifier and band pass filter circuits. These circuits have an op-amp design that is considered a basic incorporated circuit in their design, while the band pass filter can be operated by utilizing one of the op-amp's circuits or a digital filter can be used. The op-amp is usually based on Metal Oxide Semiconductor Field Effect Transistor (MOSFET) technology (see Figure 2(a)). There are several different strategies and methods for designing an op-amp [8,9]. These strategies are based

on the performance and attributes required for signal amplification in an electronic integrated circuit.

A large portion of these designs utilize the gate terminal as input node, as can be seen in Figure 2 (b). It requires a high voltage to achieve the required performance, which prompts an increase in power consumption, thus reducing the battery life. Thus, the bulk terminal is used as input signal for the MOSFET circuit (see Figure 2(c)). One of the attributes of this technique is that it produces a current regardless of whether the voltage of the gate source ( $V_{GS}$ ) is greater than the voltage threshold ( $V_{Th}$ ) or not, as it does not rely on the limit voltage.

Power supply reduction may reduce the input voltage range and, even worse, its linearity [10] and the frequency response. This can be overcome by applying a bulk-driven technique, however, the frequency response will still remain challenging. The drawbacks and benefits of bulk-driven MOSFETs are both clear. The V<sub>Th</sub> requirement in the signal path is avoided by bulk-driven MOSFET supporting features, hence increasing voltage swings under decreased voltage-power operation. However, bulk-driven MOSFETs have disadvantages such as transconductance of the body (bulk) (gmb) around five times smaller than the transconductance of the gate (gm). This makes it possible to reduce the unit gain frequency (UGF) value when UGF affects the frequency response performance. In addition, this structure also has large parasitic capacitance and high input noise [1112], which also contributes to reduction of UGF and PM.

Figure 2 (a) Structure of the MOSFET, (b) simple gate-driven PMOS, (c) conventional bulk-driven PMOS.

Miller compensation or Miller capacitance is a technique used in many op-amp designs to improve the stability (phase margin PM) in a closed loop configuration. However, it causes reduction of the frequency response, so the input node and the output node are connected with a normal capacitor (Cc) [11, 13, 14], creating Miller compensation. Another compensation technique is negative Miller compensation, which is utilized to improve UGF by reducing or

removing parasitic capacitance at the input nodes. At high frequencies, particularly for transistor capacity, their impact is noticeable since unwanted phase changes may occur that are not observed at lower frequencies.

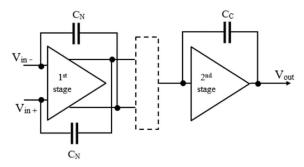

The aim of the present work was to improve the frequency response (UGF) and margin stability (PM) for low-voltage low-power bulk-driven CMOS op-amps by applying and combining two compensation techniques. Figure 3 presents a diagram of the proposed work. Two stages were designed, where the first stage is a bulk-driven differential input stage and the second stage provides additional open loop gain (DC gain). Standard Miller capacitance is connected in the second stage (see Figure 3) to provide stabilization (PM). Negative Miller capacitance is connected in the differential input stage to increase UGF. The obtainable op-amp was simulated in  $0.25\mu m$  CMOS technology; the results are shown using the standard model libraries from Tanner EDA tools. The power supply operation was reduced to +0.8 V.

**Figure 3** Op-amp diagram of the two-stage Miller compensation (standard  $(C_c)$  Miller and negative Miller  $(C_N)$  compensation).

The rest of this paper is organized as follows. In Section 2, on the basis of bulk CMOS technology, the traditional two-stage amplification technique is presented, including organizational theory, key benefits and technological consequences. Section 3 shows the compensation techniques established with the standard Miller and negative Miller compensation designs. Section 4 presents the simulation and its results, including their evaluation. Lastly, Section 5 concludes the paper.

#### 2 Standard Bulk-Driven Folded Cascode Technique

Bulk-driven CMOS blends low-voltage and low-power ICs and tends to be a beneficial strategy. Compatibility with the traditional CMOS process [15,16] is the primary benefit of this technology. The configuration of the typical MOS

transistor is not modified. In the equivalent, the need to solve the MOS transistor input  $V_{GS} > V_{Th}$  voltages is suppressed, improving the voltage headroom. MOS transistors are used as signal input for the bulk node, while the gates are fitted with  $V_{BIAS}$  voltage. To explain further, the theory of the technique is the configuration of the MOS transistor itself. There are four nodes in total: gate, drain, source, and bulk. As described in Figure 2, the system uses the bulk as the signal input ( $V_{in}$ ), which ensures that the MOS transistor input threshold voltage is surpassed [17], where a bulk-to-source junction may function under condition of negative, zero, or positive bias [18]. This will contribute to a larger input common mode voltage range, in addition to voltage swing, which otherwise cannot be accomplished with low voltage supply.

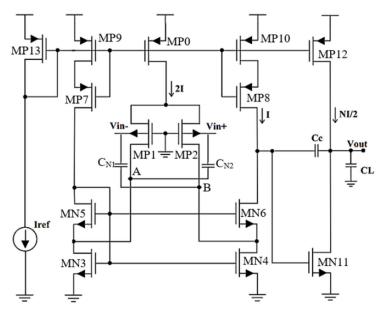

**Figure 4** Diagram of the suggested standard two-stage bulk-driven folded cascode op-amp with negative Miller compensation  $(C_N)$ .

The standard two-stage Bulk-Driven-Folded Cascode (BD-FC) op-amp was first proposed in Ref. [10]. Figure 4 shows the proposed circuit architecture for this work. The first stage consists of transistors MN1 and MN2 and the second stage is presented by MN11 and MP12. The input signals are also shown. Since transistors MN3 and MN4 are typically used as biased current sources at the initial stage of the Folded Cascode Operational Transconductance Amplifier (FC-OTA), the effective g<sub>m</sub> can be better exploited. Furthermore, the transistors MN3 and MN4 (MP1 and MP2) can be used as the driving transistors [19]. The

transistors MN3 and MN4 are also fitted with the highest DC current for the largest g<sub>m</sub>. The input signal for these transistors will then be used to further improve the transconductance [20]. If the transistor current (MP0) is 2I, the input transistor current (MP1 and MP2) is I. The transistors of the tail current need high input resistance, low noise, and low offset. It also has an effect on the UGF to reach a certain g<sub>m</sub> as well as g<sub>mb</sub>. The control g<sub>mb</sub> of the input stages is due to the tail current.

### 3 Compensation and Stability Techniques

The open-loop design can then have a phase margin of 45° or greater, which can be accomplished by the use of a compensation technique. Different compensation techniques, such as standard Miller and negative Miller compensation, may be utilized to provide the required frequency response and stability. These compensation strategies may be used alone or in combination.

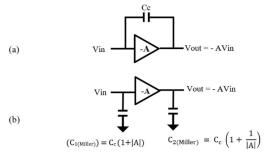

## 3.1 Standard Miller Compensation

The compensation [21] (or Miller) effect is based on the following principle: the gain (A) of the inverting amplifier is defined as negative and the feedback capacity is set between the output and the input, as shown in Figure 5 (a). Input capacitance node ( $C_{1(Miller)}$ ) and output capacitance node ( $C_{2(Miller)}$ ) with regard to ground are shown as the Miller effect, as shown in Figure 5(b). Input and output are influenced by the capacitance. The capacitance effect of the input is ( $C_{1(Miller)}$ ) =  $C_{C}$  (1+|A|). The output capacitance effect is closer to  $C_{C}$  [14] and is provided by ( $C_{2(Miller)}$ ) =  $C_{C}$  (1+1/|A|).

Figure 5 (a) Inverting amplifier with regular capacitor, (b) standard Miller theory equivalent circuit.

According to the bulk-driven op-amp structure in Figure 4, the output node (drains of MP12 and MN11) of the second stage is connected to a Miller capacitator (Cc) and the output node of the first stage (drains of MP8 and MN6). In other words, the Miller compensation capacitor (Cc) is connected in parallel

with the second stage [14], resulting in a two-stage bulk-driven CMOS op-amp, which is commonly known to have two poles [22,23]. The Miller compensation technology moves the first low-frequency pole (p1) to the origin (to the lower frequency), which makes the pole more dominant. In addition, the second high-frequency pole (p2), which is separated from the origin (to the higher frequency), becomes less dominant, creating a bandwidth far greater than that reached by connecting one node to the ground through the compensation capacitor [24]. This is aimed at attaining a suitable PM by forcing the system transfer function to behave identical to a single-pole system. The signal from the output to the input is then compensated by a feedback capacitance. However, this results in a positive zero [25] in the RHP (right hand plane) and slows down the speed of operation (UGF).

### 3.2 Negative Miller Compensation

The ability to have negative Miller compensation is based on the Miller effect. A noninverting amplifier as identified in [26] can be used to achieve negative Miller compensation. The influence of negative Miller compensation can be seen in Figure 6, in which A is the amplifier gain. The Miller effect causes a negative capacitance value at the amplification stage's input node, with a gain greater than 1 (unit) (see Figure 6(b)). The input capacitance of the amplifier is given by:

$$C_{in} = C_{bs} + C_{bsub} + C_{bd} \tag{1}$$

In addition, the equivalent input capacitance of negative Miller compensation (Eq. (2)), when the gain is greater than 1, the equivalent input capacitance ( $C_{1(NM)}$ ) is a negative value, which is called the negative capacitance:

**Figure 6** (a) Non-inverting amplifier with regular capacitor, (b) corresponding circuit of negative Miller compensation.

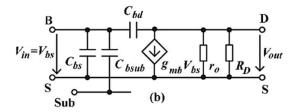

The parasitic capacitance of a bulk-driven-NMOS is presented in Figure 1(a) with the purpose of promoting the knowledge of the small signal model of the bulk-driven NMOS common source and the impact of parasitic capacitance on the parameters of the bulk-driven NMOS, as mentioned in Ref. [27]. Figure 7 shows the small signal equivalent circuit of the common source amplifier dependent bulk-driven NMOS at high frequencies. The UGF of the bulk input stage is therefore provided by:

$$UGF_b = \frac{1}{2\pi} \frac{g_{mb}}{c_{bs} + c_{bsub} + c_{bd}}$$

(3)

where, C<sub>bs</sub>, C<sub>bsub</sub> and C<sub>bd</sub> are the bulk-source, bulk-substrate and bulk-drain parasitic capacitances, respectively. The parasitic capacitances are caused by the transistor well and substrate structure. In Figure 7, the C<sub>bd</sub> capacitance provides feedback between the bulk (input node) and the drain (output node) [14].

Figure 7 Bulk-driven input DC small-signal equivalent circuit [27].

However, Cbd provides the Miller effect, decreasing the operating speed (UGF), while Cbd boosts the input capacitance and reduces the capacitance of the output counterpart. The Miller effect (transistor at input node) must be canceled or at least minimized in order to increase UGF at a high frequency. By using Eqs. (2) and (3), the value of the input capacitance (Cbs+ Cbsub+ Cbd) will be reduced by adding negative capacitance (-ClNM and UGF is given:

$$UGF_{b} = \frac{1}{2\pi} \frac{g_{mb}}{(C_{bs} + C_{bsub} + C_{bd}) + (-C_{1(NM)})}$$

(4)

#### 4 Simulation and Results

Figure 4 shows the first op-amp, which is a bulk-driven op-amp that only employs standard Miller compensation, and the second op-amp, which is a bulk-driven op-amp that uses both standard Miller and negative capacitance. Adding a capacitor to the input transistor stage is necessary to generate negative Miller capacitance.  $C_{N1}$  is attached between the input transistor level (the inverting node  $(V_{IN-})$ ) and the output node of the first stage (node (B)), while  $C_{N2}$  is attached between the non-inverting node  $(V_{IN-})$  and the input transistor stage output node (node (A)).

The op-amp architecture was developed using CMOS technologies using the standard model libraries from Tanner EDA tools at 0.25  $\mu m$  and was simulated using corner analysis (typical-typical (TT), fast-fast (FF), slow-slow (SS), slow-fast (SF) and fast-slow (FS)). For this production process, the voltage supply (Vdd) operation is usually +2.5 V, but the supply voltage in this process was reduced to +0.8 V. Table 1 lists the transistor sizes as well as the other components used in the simulation of the bulk-driven op-amp. Table 2 shows the frequency response of the op-amp using only Miller compensation (i.e., no negative Miller capacitors incorporated).

Table 1

Transistors and other elements of the bulk-driven op-amp.

| Transistor                    | Type        | Width/length |

|-------------------------------|-------------|--------------|

| MP0 (μm/ μm)                  | PMOS        | 16.10/2.5    |

| MP1, MP2( $\mu$ m/ $\mu$ m)   | PMOS        | 20.6/ 3.25   |

| MN3, MN4 ( $\mu$ m/ $\mu$ m)  | NMOS        | 20.2/5       |

| MN5, MN6 ( $\mu$ m/ $\mu$ m)  | NMOS        | 1.25/1.5     |

| MP7, MP8 ( $\mu$ m/ $\mu$ m)  | <b>PMOS</b> | 15/5         |

| MP9, MP10 ( $\mu$ m/ $\mu$ m) | <b>PMOS</b> | 35/0.25      |

| MN11 ( $\mu$ m/ $\mu$ m)      | NMOS        | 1.5/2.5      |

| MP12 ( $\mu$ m/ $\mu$ m)      | PMOS        | 6.75/2.5     |

| MP13 ( $\mu$ m/ $\mu$ m)      | PMOS        | 5/2.5        |

| Cc (fF)                       |             | 200          |

| CN (fF)                       |             | 600          |

| Iref (nA)                     |             | 140          |

**Table 2** Different Miller capacitor values for the configuration of the first opamp design.

| Cc   | DC gain | UGF    | PM       | Power consumption |

|------|---------|--------|----------|-------------------|

| (fF) | (dB)    | (kHz)  | (degree) | $(\mu W)$         |

| 0    | 63.13   | 2954.2 | -15.32   | 0.996             |

| 200  | 63.13   | 184.43 | 75.81    | 0.996             |

| 400  | 63.13   | 93.88  | 80.92    | 0.996             |

| 600  | 63.13   | 62.58  | 82.77    | 0.996             |

| 800  | 63.13   | 47.21  | 83.66    | 0.996             |

| 1000 | 63.13   | 37.79  | 84.23    | 0.996             |

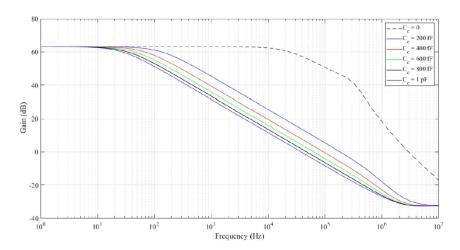

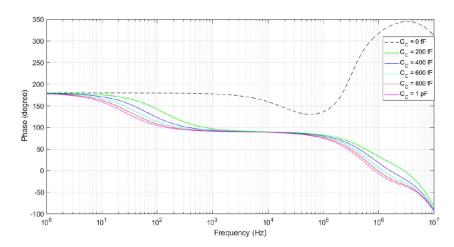

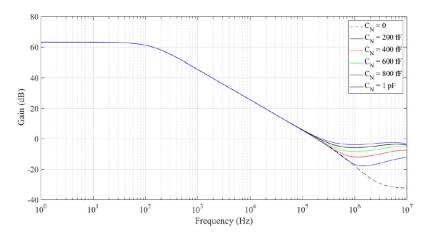

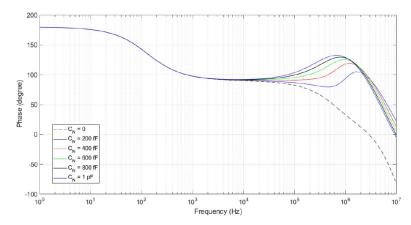

Capacitor C<sub>c</sub> varied from 0 pF (no compensation) to 1 pF and it was found that PM increased with increased Miller compensation (increasing the value of Cc), however, UGF decreased. DC gain and power consumption held the same values with Cc changing. The gain frequency and PM for various Miller capacitance values are shown in Figures 8 and 9 respectively.

**Figure 8** Frequency response diagram (open-loop op-amp gain magnitude) (no output load ( $V_{dd}$  = +0.8 V)) for the first op-amp.

Figure 9 Frequency response diagram (open-loop op-amp phase) (no output load ( $V_{dd}$ =  $\pm$  0.8 V)) for the first op-amp.

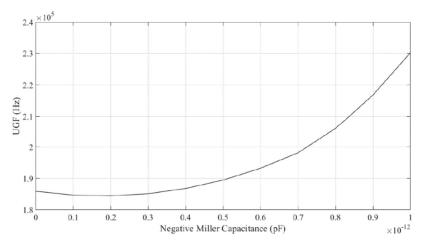

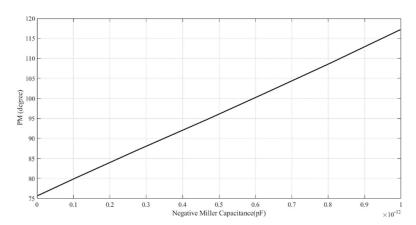

As the next step in this work, the various values of  $C_N$  with a fixed  $C_c$  value of 200 fF are shown in Table 3. As the value of  $C_N$  increased, UGF increased while PM also showed an increase. DC gain and power consumption kept very similar values with  $C_N$  changing. Figures 10 and 11 show the frequency and phase of gain for various capacitances of the negative Miller capacitator.

**Table 3** The second op-amp design with different negative Miller capacitor values (fixed Miller capacitor value = 200 fF).

| C <sub>N</sub> | DC Gain | UGF    | PM       | Power consumption |

|----------------|---------|--------|----------|-------------------|

| (fF)           | (dB)    | (kHz)  | (degree) | $(\mu W)$         |

| 0              | 63.14   | 185.90 | 75.73    | 0.99              |

| 200            | 63.14   | 184.43 | 83.98    | 0.99              |

| 400            | 63.14   | 186.78 | 92.10    | 0.99              |

| 600            | 63.14   | 193.22 | 100.23   | 0.99              |

| 800            | 63.14   | 206.06 | 108.54   | 0.99              |

| 1p             | 63.13   | 230.21 | 117.27   | 0.99              |

**Figure 10** Frequency response diagram (open-loop op-amp gain magnitude) (no output load ( $V_{dd}$ = +0.8 V)) for the second op-amp design.

Figure 11 Frequency response diagram (open-loop op-amp phase) (no output load ( $V_{dd}$ = +0.8 V)) for the second op-amp design.

A comparison of the first and second op-amp is shown in Table 4.

**Table 4** Comparison of op-amp performance: first and second op-amp design (no output load ( $V_{dd} = +0.8 \text{ V}$ )).

|                        | First op-amp<br>(Cc= 200 fF) | Second op-amp<br>(Cc= 200fF within C <sub>N</sub> = 600fF) |  |  |  |

|------------------------|------------------------------|------------------------------------------------------------|--|--|--|

| Power supply (V)       | 0.8                          | 0.8                                                        |  |  |  |

| Technology (µm)        | 0.25                         | 0.25                                                       |  |  |  |

| DC gain (dB)           | 63.14                        | 63.14                                                      |  |  |  |

| UFG (kHz)              | 181.9                        | 193.10                                                     |  |  |  |

| PM (degree)            | 75.73                        | 100.1195                                                   |  |  |  |

| Power consumption (µW) | 0.99                         | 0.99                                                       |  |  |  |

| High output swing (V)  | 0.795                        | 0.795                                                      |  |  |  |

| Low output swing (V)   | 0.018                        | 0.018                                                      |  |  |  |

| CMRR (dB)              | 108.86                       | 108.86                                                     |  |  |  |

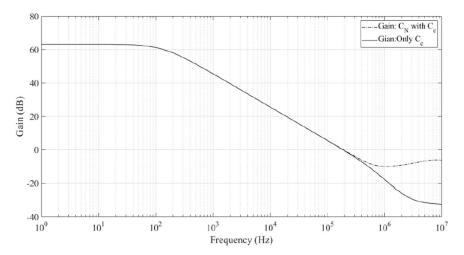

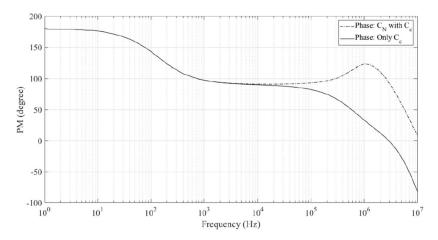

Additionally, the simulation results were evaluated without output load. Only UGF and PM were different, while all the other parameters stayed the same. Figures 12 and 13 show a comparison of the first and the second op-amp output for op-amp gain and phase, respectively.

Figure 12 Comparison of op-amp gain performance: first and second op-amp design (no output load ( $V_{dd}$ = +0.8 V)).

Figure 13 Comparison of op-amp phase performance: first and second op-amp design (no output load ( $V_{dd}$ = +0.8 V)).

The negative Miller capacitance difference with unit gain frequency for the second op-amp is presented in Figure 14; it varied from 0 pF (no negative Miller capacitor, etc.) to 1 pF. The UGF ranged from 185 kHz to around 230 kHz. The same difference was used with negative Miller capacitor to vary with the phase margin. The outcome of phase margin varied from 76° to around 117°, as can be seen in Figure 15.

Figure 14 Negative Miller capacitance variation with unity gain frequency (second op-amp).

**Figure 15** Negative Miller capacitance variation with phase margin (second opamp).

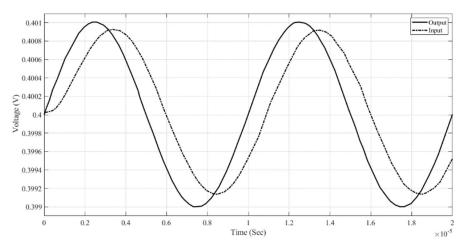

The simulated output and input waveforms of the second op-amp are shown in Figure 16 as a voltage follower circuit, at 100 kHz and 0.1 mV input sinusoidal wave amplitude. This figure shows that an input/output swing for rail-to-rail is attainable. The simulation results for the corner analysis (SS, FF, SF and FS) variations are given in Table 5 to show the global process variations on key requirements of the aimed bulk-driven op-amp. Different load capacitors were applied, as presented in Table 5.

Figure 16 The input/output signals of the second op-amp with rail-to-rail input signal at 100 kHz and amplitude 0.1 mV.

**Table 5** Review of corner analysis open-loop frequency response and power consumption for second op-amp (Cc = 200 fF, CN=600 fF,  $V_{dd} = +0.8 \text{ V}$ ).

| Corner analysis        |        |        |        |        | Load variations      |                      |  |

|------------------------|--------|--------|--------|--------|----------------------|----------------------|--|

| Corner analysis        | SS     | FF     | SF     | FS     | C <sub>L</sub> =1 pF | C <sub>L</sub> =5 pF |  |

| DC gain (dB)           | 62.34  | 60.79  | 62.71  | 54.56  | 59.88                | 59.88                |  |

| UFG (kHz)              | 173.68 | 225.03 | 207.69 | 188.86 | 406.01               | 300.16               |  |

| PM (degree)            | 99.27  | 100.80 | 95.95  | 98.07  | 67.08                | 40.43                |  |

| Power consumption (µW) | 0.999  | 0.994  | 0.99   | 1      | 6.76                 | 6.76                 |  |

The performance of the simulated second op-amp was evaluated to six published op-amp designs functioning at varied power supply voltages and different technology processes, as shown in Table 6.

**Table 6** Performance of bulk-driven op-amp with negative Miller compensation in comparison with other works.

|                         | Proposed | [10]  | [28] | [29] | [30] | [31] | [32] |

|-------------------------|----------|-------|------|------|------|------|------|

| Power supply (V)        | 0.8      | 0.6   | 0.8  | 0.9  | ±0.5 | 0.5  | 0.8  |

| Technology (µm)         | 0.25     | 0.18  | 0.18 | 0.18 | 0.35 | 0.18 | 0.18 |

| DC gain (dB)            | 63.14    | 82    | 56   | 58.4 | 59.1 | 52   | 68   |

| UFG (kHz)               | 193.10   | 19.1  | 3200 | 5150 | 5900 | 2500 | 8100 |

| Input bias current (nA) | 730      | -     | -    | <1   | 2.15 |      | -    |

| Output load (pF)        | 5        | -     | 20   | -    | -    | 20   | 1    |

| PM (degree)             | 100.2    | 60    | 45   | 71   | 63   | 45   | 89   |

| CMRR (dB)               | 108.86   | 130.2 | 100  | 55.6 | 70.5 | 78   | -    |

| High output swing (V)   | 0.795    | 560   | -    | -    | -    | -    | -    |

| Low output swing (V)    | 0.018    | 40    | -    | -    | -    | -    | -    |

| Power consumption (µW)  | 0.99     | 0.4   | 100  | 261  | 197  | 110  | 94   |

Typical process parameters and no output load were used to get the simulated results. Using typical  $0.25~\mu m$  CMOS technology, the design blends negative Miller and standard Miller compensation, showing an increase in frequency performance at a power supply voltage 0.8~V. Previous other op-amp designs [10, 28-32], which were intended for specific purposes, were also compared.

#### 5 Conclusions

Two bulk-driven op-amp architectures were implemented and evaluated in the present paper. The op-amps were planned to apply the  $0.25~\mu m$  CMOS process. Both op-amp schemes were operated at +0.8~V power supply voltage. Techniques of standard and negative Miller compensation were proposed. The first bulk-driven op-amp was compensated employing standard Miller compensation. The second bulk-driven op-amp was compensated using standard and negative Miller compensation. Simulation results were obtained using the standard model libraries from Tanner's EDA tools. The second op-amp model showed a

considerable improvement in UGF and PM while keeping power consumption constant. Future research will look at design layout difficulties such as evaluating the design performance with layout-induced parasitic aspects (both resistance and capacitance). Before the concept can be produced and actual prototypes tested, further evaluation is required.

#### Acknowledgement

The author would like to thank the Department of Radiology & Sonar, Al-Manara College for Medical Sciences for funding this project.

#### References

- [1] Nashirul Haq, I., Kurniadi, D., Leksono, E., Yuliarto, B. & Soelami, F., Performance Analysis of Energy Storage in Smart Microgrid Based on Historical Data of Individual Battery Temperature and Voltage Changes. Journal of Engineering and Technological Sciences, **51**, pp. 149-169, 2019. DOI: 10.5614/j.eng.technol.sci.2019.51.2.1.

- [2] Fariborzi, H., Moghavvemi, M. & Mehrkanoon, S., Design of a Low-power Microcontroller-based Wireless ECG Monitoring System. in 2007 5<sup>th</sup> Student Conference on Research and Development, 2007. DOI: 10.1109/SCORED.2007.4451383.

- [3] Ahamed, M.A., Hasan, M.K. & Alam, M.S., *Design and Implementation of Low-cost ECG Monitoring System for the Patient Using Smartphone* in 2015 International Conference on Electrical & Electronic Engineering (ICEEE), 2015. DOI: 10.1109/CEEE.2015.7428272.

- [4] Wang, K., Ma, S., Feng, J., Zhang, W., Fan, M. & Zhao, D., *Design of ECG Signal Acquisition System Based on DSP*, Procedia Engineering, **29**, pp. 3763-3767, 2012. DOI: 10.1016/j.proeng.2012.01.567.

- [5] Egila, M.G., El-Moursy, M.A. & El-Hennawy, A.E., FPGA-based Electrocardiography (ECG) Signal Analysis System Using Least-Square Linear Phase Finite Impulse Response (FIR) Filter, Journal of Electrical Systems and Information Technology, **3**(3), pp. 513-526, 2016. DOI: 10.1016/j.jesit.2015.07.001.

- [6] Dubey, A.K., Srivastava, P. & Pattanaik, M., Efficient Technique to Reduce Power Dissipation of Op-Amps at High Speed, in 2015 International Conference on Robotics, Automation, Control and Embedded Systems (RACE), 2015. DOI:10.1109/RACE.2015.7097292.

- [7] Zaidi, M., Grout, I. & A'ain, A.K. Programmable Gain and Bandwidth Op-Amp Using Controllable Input Stage Tail Current, in 2018 International Electrical Engineering Congress (iEECON), 2018. DOI: 10.1109/IEECON.2018.8712233.

- [8] Gupta, A., Chandrawat, U. B. S., Mishra, D. K., Khatri, R. & Jain, P., A Two Stage and Three Stage CMOS OPAMP with Fast Settling, High DC Gain and Low Power Designed in 180nm Technology, in 2010 International Conference on Computer Information Systems and Industrial Management Applications (CISIM), 2010. DOI: 10.1109/CISIM.2010.5643497.

- [9] Jahangir, M.Z. & Paidimarry, C.S., *Design of Programmable Op-Amps with Minimized DC Variations at Output*, in 2013 IEEE Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics (PrimeAsia), 2013. DOI: 10.1109/PrimeAsia.2013.6731190.

- [10] Akbari, M. & Hashemipour, O., A 63-dB Gain OTA Operating in Subthreshold with 20-nW Power Consumption, International Journal of Circuit Theory and Applications, 45(6), pp. 843-850, 2016. DOI:10.1002/cta.2248.

- [11] Zaidi, M., Design and Evaluation of High-Speed Operational Amplifier Designs Using the Negative Miller Capacitance Design Technique, 2018.

- [12] Dahono, P., Amirudin, D., Rizqiawan, A. & Deni, D., *Analysis of Input and Output Ripples of PWM AC Choppers*, ITB Journal of Engineering Science, **40**, pp. 91-109, 2008. DOI: 10.5614/itbj.eng.sci.2008.40.2.2.

- [13] Arici, I.S. & Gökcen, D., *The Effects of Direct and Indirect Compensation Techniques on the Specifications of Operational Amplifiers*, in 2019 27<sup>th</sup> Signal Processing and Communications Applications Conference (SIU). 2019.

- [14] Zaidi, M., Grout, I. & A'ain, A.K.. Evaluation of Compensation Techniques for CMOS Operational Amplifier Design, in 2018 International Conference on IC Design & Technology (ICICDT), 2018. DOI: 10.1109/ICICDT.2018.8399722.

- [15] Rakús, M., Stopjakova, V. & Arbet, D., Design Techniques for Low-Voltage Analog Integrated Circuits, Journal of Electrical Engineering, 68(4), No. 245-255, 2017. DOI: 10.1515/jee-2017-0036.

- [16] Syahriar, A., Wulandari, P., Lubis, A., Wigajatri, R., Gandana, D & Mujadin, A., The Method of Lines Analysis of TE Mode Propagation in Silica based Optical Directional Couplers, Journal of Engineering and Technological Sciences, 53, 210302, 2021. DOI: 10.5614/j.eng.technol.sci.2021.53.3.2.

- [17] Tai, C.-F., Lai, J.-L. & Chen, R.-J., Using Bulk-driven Technology Operate in Subthreshold Region to Design a Low Voltage and Low Current Operational Amplifier, pp. 1-5, 2006.

- [18] Masoom, A. & Hadidi, K., A 1.5-V, Constant-Gm, Rail-to-Rail Input Stage Operational Amplifier. in 2006 13<sup>th</sup> IEEE International Conference on Electronics, Circuits and Systems, 2006. DOI: 10.1109/ICECS.2006.379868.

- [19] Ghaemnia, A. & Hashemipour, O., *An Ultra-low Power High Gain CMOS OTA for Biomedical Applications*, Analog Integrated Circuits and Signal Processing, **99**(3), pp. 529-537, 2019. DOI:10.1007/s10470-019-01438-6.

- [20] Akbari, M. & Hashemipour, O., Enhancing Transconductance of Ultralow-Power Two-Stage Folded Cascode OTA, Electronics Letters, 50, pp. 1514-1516, 2014. DOI:10.1049/el.2014.2399.

- [21] Abdulaziz, M., Törmänen, M. & Sjöland, H., A Compensation Technique for Two-stage Differential OTAs, IEEE Transactions on Circuits and Systems II: Express Briefs, **61**(8), pp. 594-598, 2014. DOI: 10.1109/TCSII.2014.2327475.

- [22] Kim, H., Park, Y., Yang, H. & Kim, S., A Constant Bandwidth Switched-Capacitor Programmable-Gain Amplifier Utilizing Adaptive Miller Compensation Technique, in 2017 30th IEEE International System-on-Chip Conference (SOCC), 2017. DOI:10.1109/SOCC.2017.8226051

- [23] Hurst, P.J., Lewis, S.H., Keane, J.P., Aram, F. & Dyer, K.C., *Miller Compensation Using Current Buffers in Fully Differential CMOS Two-stage Operational Amplifiers*, IEEE Transactions on Circuits and Systems I: Regular Papers, **51**(2), pp. 275-285, 2004. DOI: 10.1109/TCSI.2003.820254.

- [24] Razavi, B., Design of Analog CMOS Integrated Circuits, McGraw-Hill, Inc. 704, 2001.

- [25] Nagulapalli, R., Hayatleh, K., Barker, S., Zourob, S., Yassine, N. & Kumar, B.N., *A Technique to Reduce the Capacitor Size in Two Stage Miller Compensated Opamp*, in 2018 9<sup>th</sup> International Conference on Computing, Communication and Networking Technologies (ICCCNT), 2018. DOI:10.1109/ICCCNT.2018.8493494

- [26] Genz, A.P., Operational Amplifier Bandwidth Extension Using Negative Capacitance Generation, 2006.

- [27] Khateb, F., Bay, S., Dabbous, A. & Vlassis, S., A Survey of Non-conventional Techniques for Low-voltage Low-power Analog Circuit Design, Radioengineering, 2013, 22.

- [28] Raikos, G. & S. Vlassis, 0.8 V Bulk-driven Operational Amplifier, Analog Integrated Circuits and Signal Processing, 63(3), pp. 425-432, 2010. DOI:10.1007/s10470-009-9425-4.

- [29] Tang, N., Hong, W., Kim, J., Yang, Y. & Heo, D., A Sub-1-V Bulk-Driven Opamp with an Effective Transconductance-Stabilizing Technique, IEEE Transactions on Circuits and Systems II: Express Briefs, 62(11), pp. 1018-1022, 2015. DOI:10.1109/TCSII.2015.2455471.

- [30] Carrillo, J.M., Torelli, G., Valverde, R.P.-A. & Duque-Carrillo, J.F., *1-V Rail-to-Rail CMOS OpAmp With Improved Bulk-Driven Input Stage*, IEEE Journal of Solid-State Circuits, **42**(3), pp. 508-517, 2007. DOI:10.1109/JSSC.2006.891717.

- [31] Chatterjee, S., Tsividis, Y. & Kinget, P., 0.5-V Analog Circuit Techniques and Their Application in OTA and Filter Design, IEEE Journal of Solid-State Circuits, 40(12), pp. 2373-2387, 2005. DOI:10.1109/JSSC.2005. 56280

- [32] Rosenfeld, J., Kozak, M. & Friedman, E.G., *A Bulk-driven CMOS OTA with 68 dB DC Gain*, in Proceedings of the 2004 11<sup>th</sup> IEEE International Conference on Electronics, Circuits and Systems, 2004.